Floating Point Addition Algorithm In Computer Architecture

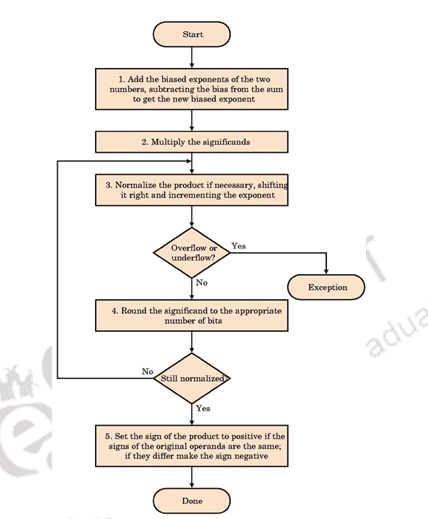

11111111001 which is a case of overflow many sources that i studied neglect this multiplication algorithm by saying that the multiplication is same as in case of fixed point numbers i think that is the only logic that can make no overflow in floating pt nos true as in multiplication we neglect the extra bit and just write our answer. For example we have to add 11 10 3 and 50.

Floating Point Arithmetic Unit Computer Architecture

Floating Point Arithmetic Unit Computer Architecture

The MIPS FP architecture uses separate floating point insturctions for IEEE 754 single and double precision.

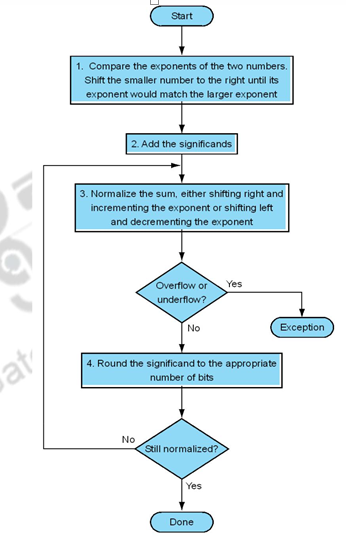

Floating point addition algorithm in computer architecture. Floating point addition - F1 x 2 E1 -F2 x 2 E2 - F3 x 2 E3 Restore the hidden bit in F1 and F2 Right shift F2 by E1-E2 positions E1E2 and the three bits shifted out are called round bit guard bit. The IEEE 754 standard defines a binary floating point format. Lec 14 Systems Architecture 18 Floating Point Arithmetic flx nearest floating point number to x Relative error precision s digits x - flxx 12 1-s for 2 2-s Arithmetic x y flxy x y1 for u x y flx y1 for u.

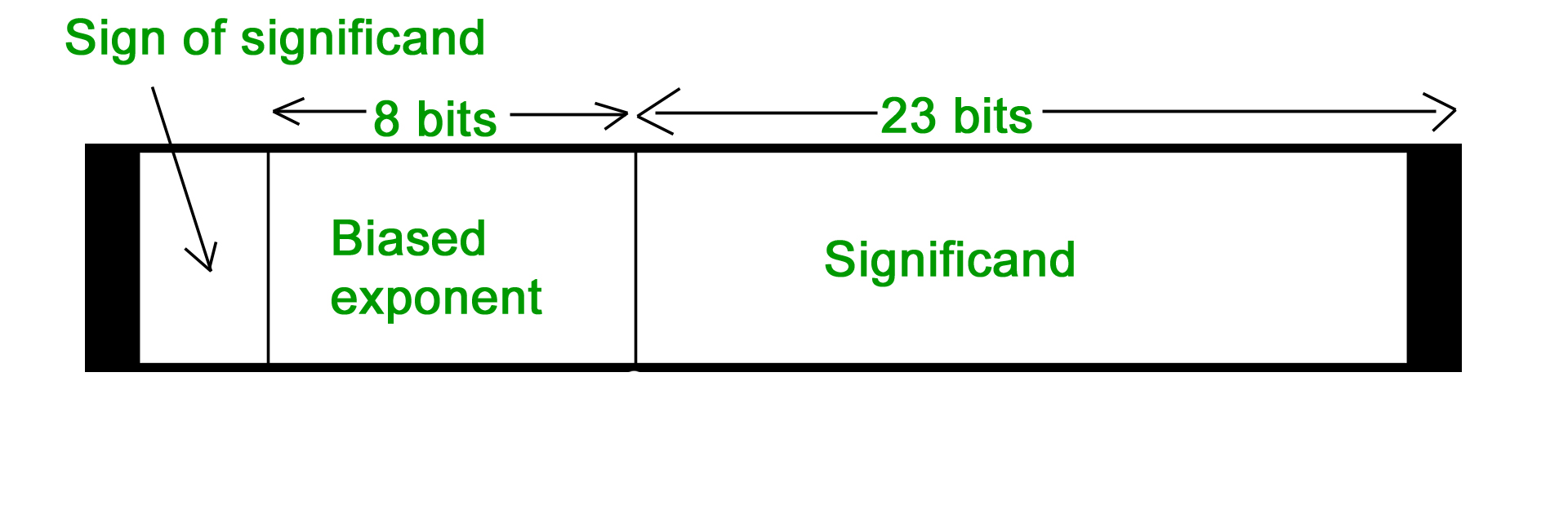

Floating Point Representation Numerical Form 1s M 2E Sign bit s determines whether number is negative or positive. Significand M is normally a fractional value in the range 1020 Exponent E weights value by power of two. Compute Ye - Xe a fixed point subtraction.

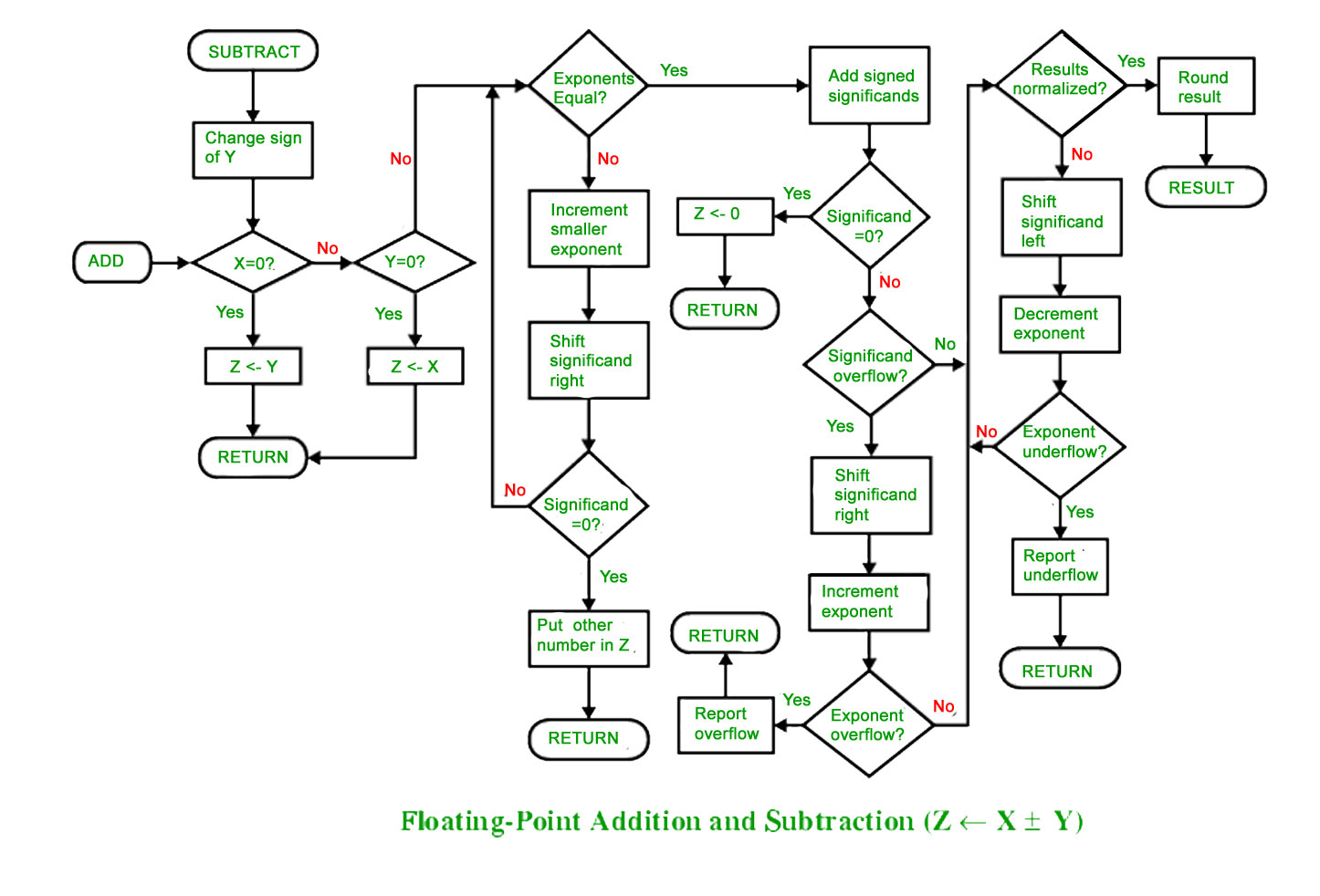

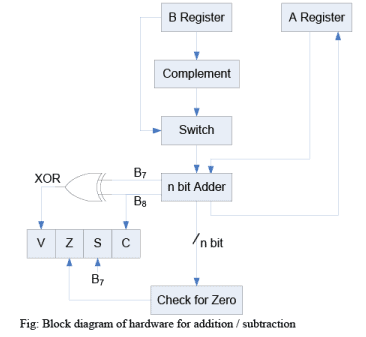

FLOATING POINT ADDITION AND SUBTRACTION. The operations are done with algorithms similar to those used on sign magnitude integers because of the similarity of representation example only add numbers of the same sign. Floating Point Addition To add two floating point values they have to be aligned so that they have the same exponent.

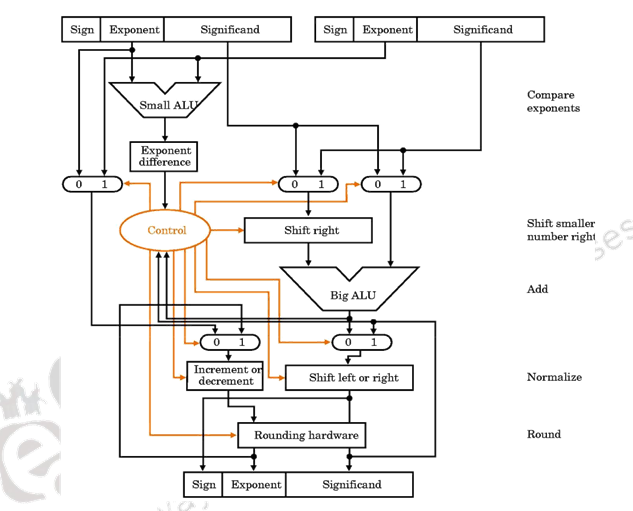

Operations with floating-point numbers Additionsubtraction. Need to have both operands with the same exponent - small ALU calculates exponent difference - Shift number with smaller exponent to the right Addsubtract the mantissas Multiplicationdivision Addsubtract the exponents. Ercegovac Tomás Lang in Digital Arithmetic 2004 846 Delay and Pipelining The delay or latency of the floating-point addition corresponds to the critical path obtained from the delay graph shown in Figure 87.

The sum of difference is formed in the AC. Floating-Point Representation Algorithms and Implementations Miloš D. Of the floating-point fvalue.

After addition the sum may need to be normalized. If the numbers are of opposite sign must do subtraction. To understand floating point addition first we see addition of real numbers in decimal as same logic is applied in both cases.

Apr 21 2021 - Addition Algorithm Subtraction Algorithm - Computer Organization and Architecture EduRev Notes is made by best teachers of Computer Science Engineering CSE. Addition and subtraction During addition and subtraction the two floating point operands are in AC and BR. Add or subtract the mantissa.

Please like subscribe for more CS based tutorials. Shift the mantissa of X m by Ye - Xe steps to the right to form X m 2 Ye-Xe if Xe is smaller than Ye else the mantissa of Y m will have to be adjusted. The architecture details are left to the hardware manufacturers.

Arithmetic operations on floating point numbers consist of addition subtraction multiplication and division. Floats 32-bit floating point numbers CS429 Slideset 4. Potential errors include overflow underflow and inexact results.

This document is highly rated by Computer Science Engineering CSE students and. The storage order of individual bytes in binary floating point numbers varies from architecture to architecture. Thanks to Venki for writing the above article.

The algorithm can be divided into four consecutive parts. 234 103 622 108 088 103 393 108. IEEE 754 Floating-Point Standard Found in virtually every computer invented since 1980 Simplified porting of floating-point numbers Unified the development of floating-point algorithms Increased the accuracy of floating-point numbers Single Precision Floating Point Numbers 32 bits 1-bit sign 8-bit exponent 23-bit fraction Double Precision Floating Point Numbers 64 bits 1-bit sign 11-bit exponent 52-bit fraction S Exponent8.

Compute X m 2 Ye-Xe Y m. I will take an example in binary. Let X and Y be the FP numbers involved in additionsubtraction where Y e X e.

Single precision uses adds subs muls and divs whereas double precision instructions are addd subd muld and divd. Please write comments if you find anything incorrect or.

Organization Of Computer Systems Computer Arithmetic

Organization Of Computer Systems Computer Arithmetic

Computer Arithmetic Set 2 Geeksforgeeks

Computer Arithmetic Set 2 Geeksforgeeks

Floating Point Arithmetic Unit Computer Architecture

Floating Point Arithmetic Unit Computer Architecture

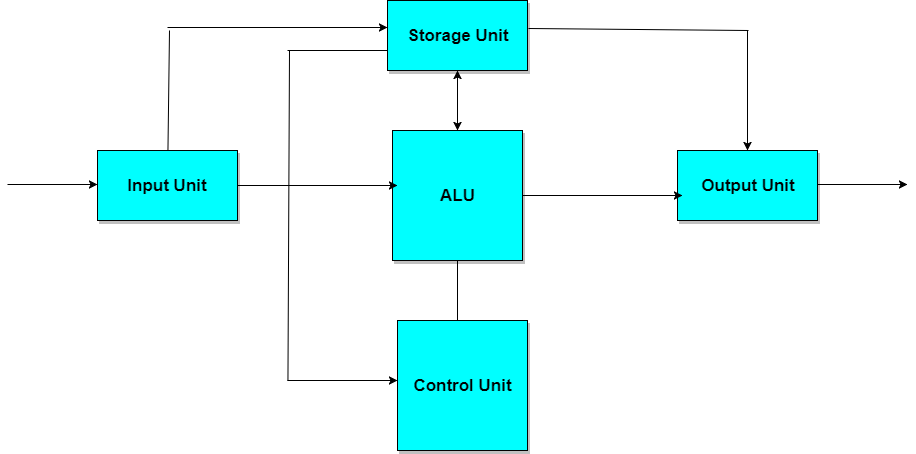

Architecture Of Computer System Computer Architecture Tutorial Studytonight

Architecture Of Computer System Computer Architecture Tutorial Studytonight

Floating Point Addition And Subtraction Youtube

Floating Point Addition And Subtraction Youtube

Floating Point Arithmetic Unit Computer Architecture

Floating Point Arithmetic Unit Computer Architecture

Organization Of Computer Systems Computer Arithmetic

Organization Of Computer Systems Computer Arithmetic

Binary Arithmetic Digital Computer Design A Hands On Approach Openstax Cnx

Binary Arithmetic Digital Computer Design A Hands On Approach Openstax Cnx

Booth S Algorithm Hardware Implementation With Example Algorithm Binary Number Positive And Negative

Booth S Algorithm Hardware Implementation With Example Algorithm Binary Number Positive And Negative

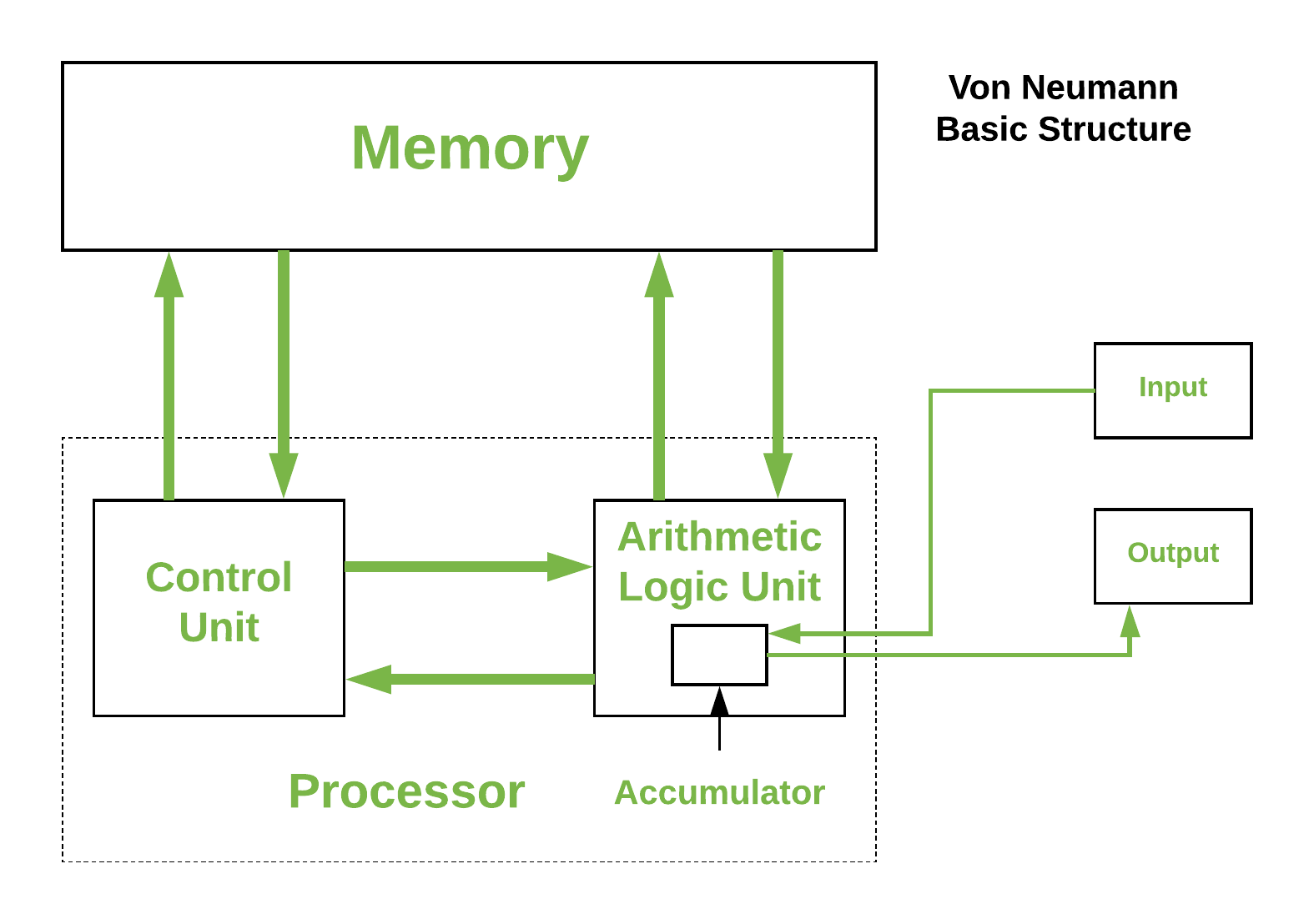

Ark Eng Fundamentals Of Computer Architecture Marek Tudruji Initial Hardware And Software Concepts Ii The Concept Of Computer Architecture Block Diagrams Architectural Models Computational Models 1 Levels For Digital Device Description 2

Ark Eng Fundamentals Of Computer Architecture Marek Tudruji Initial Hardware And Software Concepts Ii The Concept Of Computer Architecture Block Diagrams Architectural Models Computational Models 1 Levels For Digital Device Description 2

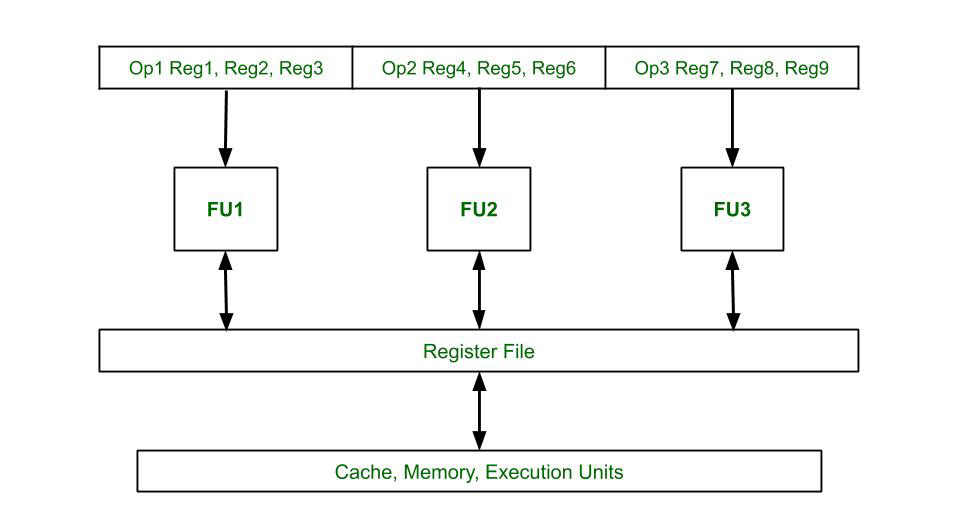

Very Long Instruction Word Vliw Architecture Geeksforgeeks

Very Long Instruction Word Vliw Architecture Geeksforgeeks

Floating Point Arithmetic Unit Computer Architecture

Floating Point Arithmetic Unit Computer Architecture

Computer Arithmetic Set 1 Geeksforgeeks

Computer Arithmetic Set 1 Geeksforgeeks

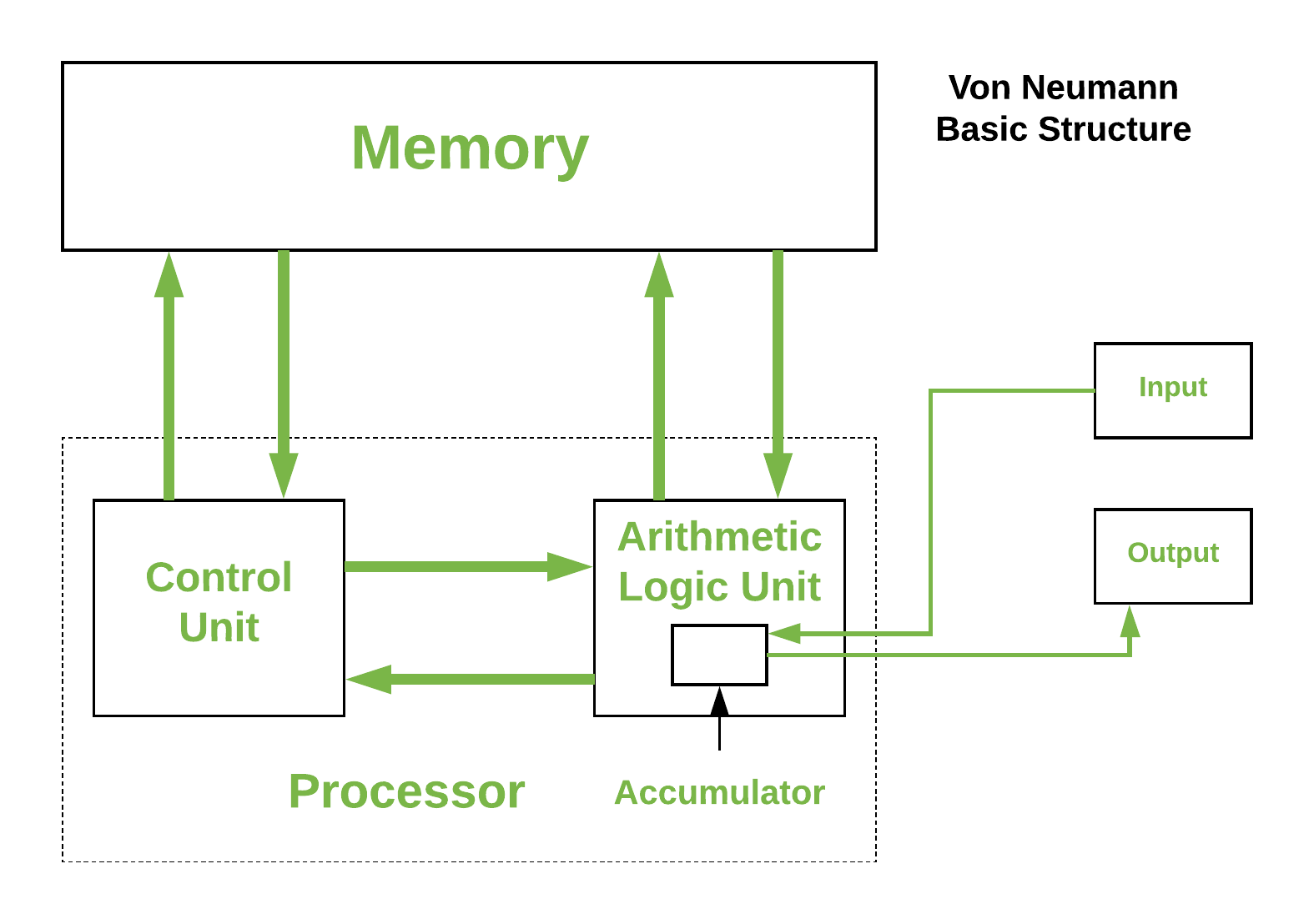

Computer Organization Von Neumann Architecture Geeksforgeeks

Computer Organization Von Neumann Architecture Geeksforgeeks

Caches And Cache Types Quizzes Computer Architecture Quiz 27 Questions And Answers P Computer Architecture Architecture Quiz Trivia Questions And Answers

Caches And Cache Types Quizzes Computer Architecture Quiz 27 Questions And Answers P Computer Architecture Architecture Quiz Trivia Questions And Answers

Organization Of Computer Systems Isa Machine Language Number Systems

Organization Of Computer Systems Isa Machine Language Number Systems