Addition And Subtraction Algorithm In Computer Architecture Ppt

Add add add immediate addi and subtract sub cause exceptions interrupt on overflow. 4 Q41A0Qs1 EAAB1011 EAQ 0 1011 0111 Shr EAQ 0 0101 1011 3 Q31 EA 1 0000 EAQ 1 0000 1011 Shr EAQ 0 1000 0101 2 Q21 EA 1 0011 EAQ 1 0011 01 01 shr EAQ 0 1001 101 0 1 Q10.

1 Computers And Systems The Architecture Of Computer Hardware System Software And Networking An Infor Information Technology Computer Hardware Technology

Second one can negate the subtrahend ie in a - b the subtrahend is b then perform addition.

Addition and subtraction algorithm in computer architecture ppt. The output carry is transferred to flip-flop E. AND OR Ex-OR Invert etc in addition to the arithmetic operations eg. Worlds Best PowerPoint Templates - CrystalGraphics offers more PowerPoint templates than anyone else in the world with over 4 million to choose from.

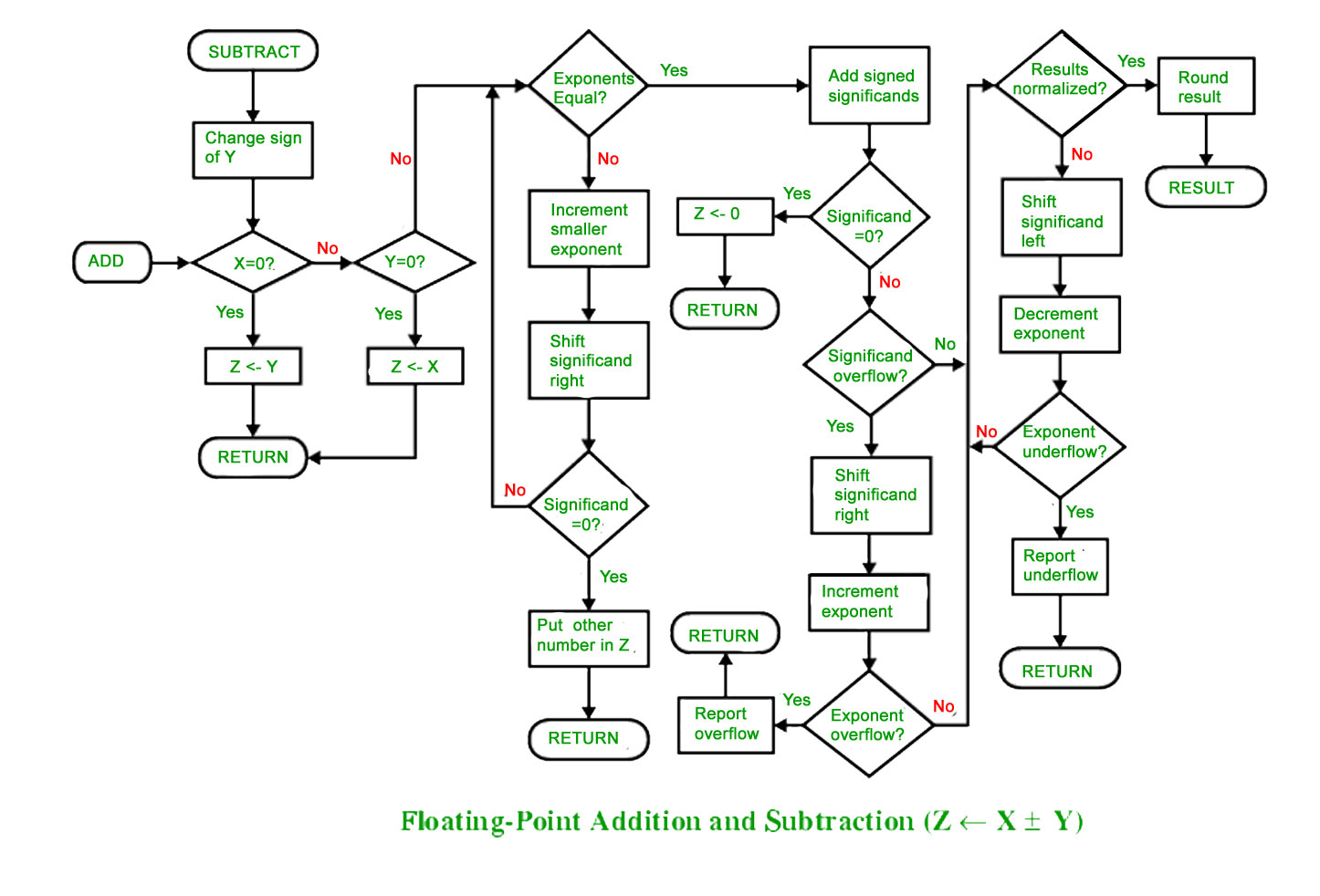

So finally we get 11 103 50 115 103. Check for zeros Align significands adjusting exponents Add or subtract significands Normalize result. Subtraction is done by adding A to the 2s complement of B.

Addition and Subtraction CE Overflow The computer designer must therefore provide a way to ignore overflow in some cases and to recognize it in others. Here notice that we shifted 50 and made it 005 to add these numbers. Let m and r be the multiplicand and multiplier respectively.

Booths algorithm can be implemented by repeatedly adding with ordinary unsigned binary addition one of two predetermined values A and S to a product P then performing a rightward arithmetic shift on P. Addition Algorithm Subtraction Algorithm - Computer Organization and Architecture EduRev Notes notes for Computer Science Engineering CSE is made by best teachers who have written some of the best books of Computer Science Engineering CSE. EngineeringDrive ComputerOrganization AdditionSubtractionIn this video the following topic is coveredCOMPUTER ORGANIZATION Part-16 Addition Subtra.

We follow these steps to add two numbers. First one can formulate a subtraction algorithm which is distinct from addition. Theyll give your presentations a professional memorable appearance - the kind of sophisticated look that todays audiences expect.

FP Arithmetic Addition Subtraction In floating-point arithmetic addition and subtraction are more complex than multiplication and division. Since we already know how to perform addition as well as twos complement negation the second alternative is more practical. Now let us take example of floating point number addition.

See the example below where case b case c and case e are worked out as 2s complement representation. Addition and Subtraction For addition use normal binary addition 00sum 0 carry 0 01sum 1 carry 0 11sum 0 carry 1 Monitor MSB for overflow Overflow cannot occur when adding 2 operands with the different signs If 2 operand have same sign and result has a different sign overflow. How to perform addition and subtraction on floating point numbers.

The initial step to this assignment was making two cubes out of Bristol paper one with volumes subtracted from a cube and one with those volumes that were subtracted. There are four basic phases of the algorithm for addition and subtraction. Of bit in multiplier Partial product.

And A-B becomes A 2s complement B. Apr 20 2021 - Addition Algorithm Subtraction Algorithm Computer Science Engineering CSE Video EduRev is made by best teachers of Computer Science Engineering CSE. Inside a computer there is an Arithmetic Logic Unit ALU which is capable of performing logical operations eg.

Helvetica Symbol Arial Black Contemporary ImagingDocument COMPUTER ARITHMETIC Chapter Organization A warning ADDITION AND SUBTRACTION General concept Realization Observations Signed and unsigned additions Signed and unsigned additions Overflow handling I Overflow handling. A control signal called SUBTRACT is used as add value of 1. Add unsigned addu add immediate.

Microcontroller Microprocessor Computers. Figure 72 shows a block diagram of the hardware for implementing the addition and subtraction operations. As I began to make more study models and developed the design of.

It has gotten 14680 views and also has 47 rating. COSC33306308 Computer Architecture Author. It consists of registers A and B and sign flip-flops As and Bs.

Addition and Subtraction cube 1. Now adding significand 005 11 115. The XOR circuit will generate 1s complement.

This video is highly rated by Computer Science Engineering. The MIPS solution is to have two kinds of arithmetic instructions to recognize the two choices. 2s complement addition and subtraction.

The control unit supplies the data required by the ALU from memory or from input devices and directs the ALU to perform a specific. This way an adder executes subtraction. Lec 14 Systems Architecture 29 FP Arithmetic Hardware FP multiplier is of similar complexity to FP adder But uses a multiplier for significands instead of an adder FP arithmetic hardware usually does Addition subtraction multiplication division reciprocal square-root FP integer conversion.

The concept of this project was to explore the relationship of spaces through the addition and subtraction of voids within a cube. Winner of the Standing Ovation Award for Best PowerPoint Templates from Presentations Magazine.

Ppt Computer Architecture Powerpoint Presentation Free Download Id 6784739

Addition Algorithm Subtraction Algorithm Computer Organization And Architecture Edurev Notes

Unit 7 Addition Subtraction Algorithm Youtube

Computer Arithmetic In Computer Architecture

Von Neumann Architecture Computer Science Gcse Guru

Addition And Subtraction Binary Arithmetic Part 1 Youtube

Project Management Transition Plan Template New Delivery Methodology Ppt Video Online High School Lesson Plans School Lesson Plans Business Plan Template

Organization Of Computer Systems Computer Arithmetic

Cmpe 325 Computer Architecture Ii Ppt Video Online Download

Addition Algorithm Subtraction Algorithm Computer Organization And Architecture Edurev Notes

Coa Booth S Multiplication Algorithm Javatpoint

Cs 404 Coa Unit Ii Computer Arithmetic Division Mathematics Multiplication

Floating Point Arithmetic Unit Computer Architecture

Computer Arithmetic Set 2 Geeksforgeeks

Floating Point Arithmetic Unit Computer Architecture

Computer Organization Von Neumann Architecture Geeksforgeeks

Chapter 3 A Top Level View Of Computer Function And Interconnection Reading Data Memory Module Pearson Education